# Design and Performance Analysis of a High-Speed Network Processor

By

Md. Jahidul Islam

Roll No: 0803507

A thesis submitted in partial fulfillment of the requirements for the degree of Master of Science in Electrical and Electronic Engineering

Khulna University of Engineering & Technology Khulna 9203, Bangladesh

August 2011

# **Declaration**

This is to certify that the thesis work entitled "Design and Performance Analysis of a High-Speed Network Processor" has been carried out by Md. Jahidul Islam in the Department of Electrical and Electronic Engineering, Khulna University of Engineering & Technology, Khulna, Bangladesh. The above thesis work or any part of this work has not been submitted anywhere for the award of any degree or diploma.

Signature of Supervisor

(Prof. Dr. Md. Abdur Rafiq)

Signature of Candidate

(Md. Jahidul Islam)

# **Approval**

This is to certify that the thesis work submitted by Md. Jahidul Islam entitled "Design and Performance Analysis of a High-Speed Network Processor" has been approved by the board of examiners for the partial fulfillment of the requirements for the degree of Master of Science in Engineering in the Department of Electrical and Electronic Engineering, Khulna University of Engineering & Technology, Khulna, Bangladesh in August 2011.

# **BOARD OF EXAMINERS**

| 1. | 27.08.11                                                                                                                                | Chairman<br>(Supervisor) |

|----|-----------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

|    | Dr. Md. Abdur Rafiq Professor Department of Electrical and Electronic Engineering Khulna University of Engineering & Technology         |                          |

| 2. | Head Department of Electrical and Electronic Engineering Khulna University of Engineering & Technology                                  | Member                   |

| 3. | Dr. Md. Rafiqul Islam Professor Department of Electrical and Electronic Engineering Khulna University of Engineering & Technology       | Member                   |

| 4. | Dr. Md. Shahjahan Associate Professor Department of Electrical and Electronic Engineering Khulna University of Engineering & Technology | Member                   |

| 5. | Dr. M. M. A. Hashem Professor Department of Computer Science and Engineering Khulna University of Engineering & Technology              | Member<br>(External)     |

# Acknowledgement

First of all, I would like to grateful to almighty ALLAH.

As a master's student I not only furthered my technical skills but also got an opportunity to enrich my professional life. I have realized the importance of patience, intellectual humility and optimism during this course of time.

I would like to sincerely thank my supervisor Professor Dr. Md. Abdur Rafiq for providing me the opportunity to work on such an interesting topic of Network Processor. He has been very encouraging and patient with me, besides giving me a lot of independence. His regular guidance, inspiration and the time providing played the vital role in completion of this thesis work. I would also like to thank him for all the long hours he spent reviewing my thesis and timely feedback, even while on vacation.

I would grateful to the researchers in the field of network processor, packet processor, networking systems, data communication, high-speed communication system and FPGA/ASIC design for their research work and recent publications.

It is mentionable that, my work would not have been possible without the necessary CAD software. So, I would like to thank EZchip microcode development tools and NepSim Network processor simulator. I specially would like to thank Xilinx Foundation for the ISE Design software tools and Actel Corporation for their Libero IDE FPGA Design tools, without which I could not have completed my work. I would also like to thank Mentor Graphics for their ModelSim waveform simulator.

Finally, I would like to thank my family for all their love and support all along this effort. Especially thanks to my parents for always having faith in my abilities and giving inspiration for successfully completion of the research work. I would also like to thank to my friends for giving mental support and encouragement that has helped me cope with difficult times.

# Abstract

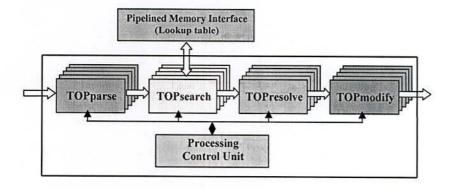

Network processor is the key architecture of the recent communication technology. Most of the high performance network equipments especially routers, switches and traffic management systems are designed with network processor to processes their network packets. This research work introduces a design architecture for high-speed network packet processor and also analyzes its performance. There are two proposals in this thesis, first is the proposed hardware architecture of a high-speed network processor system and second is the proposed modified architecture of packet processing unit. A hierarchical 4 level layered processing architecture is developed for efficiently process the packets. To capture all traffic from a high-speed I/O interface without any loss a load-balancer with an efficient load distribution algorithm is implemented. High throughput pipelined memory architecture is also developed to minimize the rate of memory access time. The processor units have four basic operational tasks - parse, search, resolve and modify. To design the processing unit, the thesis provides some modification of the Task Optimized Processing core (TOPcore) technology and proposed a modified processing core architecture. This is a super-pipelined parallel architecture. The performance of the proposed network processor is evaluated for some real applications and compared with reference NPs. Results shows that the proposed architecture is efficient and provides better performance. Finally, the design is modeled and simulated in RT level using VHDL and then synthesized to schematic. The synthesis is done for both Xilinx Spartan3 and Actel ProASIC3 FPGA. Design requires very little FPGA logic while efficiently processing packet and implementation of green technology provides saving of power consumption at ideal condition.

To my parents

# Contents

|             |                                                | PAGE     |

|-------------|------------------------------------------------|----------|

| Title Pa    | ge                                             | i        |

| Declara     | tion                                           | ii       |

| Approva     |                                                | iii      |

|             | ledgement                                      | iv       |

| Abstrac     |                                                | v        |

| Content     |                                                | vii      |

| List of     |                                                | ix       |

| List of I   | rigures                                        | X        |

| CHAPTER I   | Introduction                                   |          |

|             | 1.1 Background and Previous work               | 1        |

|             | 1.2 Motivation and Objectives                  | 2        |

|             | 1.3 Scope of the thesis                        | 3        |

|             | 1.4 Approaches                                 | 4        |

|             | 1.5 Challenges                                 | 4        |

|             | 1.6 Organization of the thesis                 | 4        |

| CHAPTER II  | Network Processor Review                       |          |

|             | 2.1 Overview                                   | 6        |

|             | 2.2 Evaluation                                 | 8        |

|             | 2.2.1 First-Generation Systems                 | 8        |

|             | 2.2.2 Second-Generation Systems                | 9        |

|             | 2.2.3 Third-Generation Systems                 | 10       |

|             | 2.3 Applications                               | 10       |

|             | 2.4 Generic Architecture                       | 12       |

| CHAPTER III | Data Networking and Packet Processing          |          |

|             | 3.1 Data Networking Models                     | 15       |

|             | 3.1.1 ISO/OSI Model                            | 15       |

|             | 3.1.2 TCP/IP Model                             | 16       |

|             | 3.1.3 Data Networking                          | 16       |

|             | 3.2 Packet Processing                          | 18       |

|             | 3.2.1 Packet Processing Flow                   | 19       |

|             | 3.2.2 Ingress and Egress                       | 20       |

|             | 3.2.3 Framing 3.2.4 Parsing and Classification | 21<br>21 |

|             | 3.2.5 IP Lookup and Forwarding                 | 22       |

|             | 3.2.6 Modification                             | 23       |

|             | 3.2.7 Compression and Encryption               | 23       |

|             | 3.2.8 Queuing and Traffic Management           | 24       |

|             | 3.3 IP Addressing, Routing and Forwarding      | 24       |

|             | 3.4 Search Engines                             | 27       |

|             | 3.4.1 Simple Switching and Forwarding          | 31       |

|             | 3.4.2 IP Address Lookup                        | 31       |

| CHAPTER IV  | Architecture and Methodology                         |    |

|-------------|------------------------------------------------------|----|

|             | 4.1 Network Processing Trends                        | 32 |

|             | 4.1.1 Network Processing Functions                   | 33 |

|             | 4.2 Architectures of Network Processor               | 34 |

|             | 4.2.1 Basic Architectural Approaches                 | 35 |

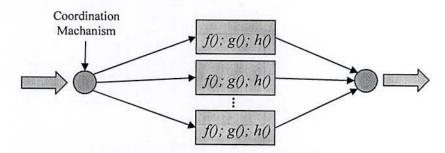

|             | 4.2.2 Parallel Pipelines of Homogeneous Processors   | 36 |

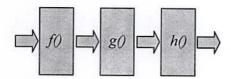

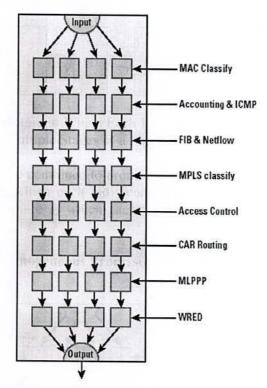

|             | 4.2.3 Pipeline of Parallel Heterogeneous Processors  | 37 |

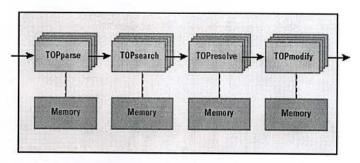

|             | 4.2.4 Superpipeline and Superscalar Architecture     | 37 |

|             | 4.3 Design Methodology                               | 38 |

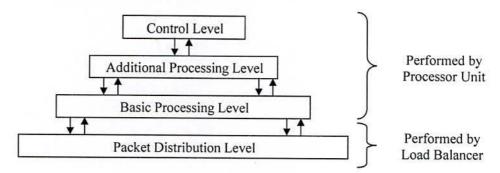

|             | 4.3.1 Layered Processing Architecture                | 38 |

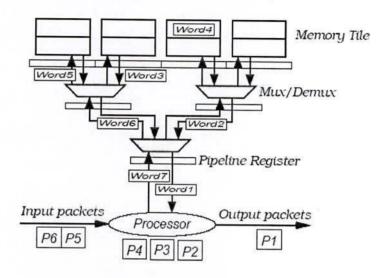

|             | 4.3.2 Pipelined Memory Architecture                  | 39 |

|             | 4.3.3 High Throughput Pipelined Memory               | 39 |

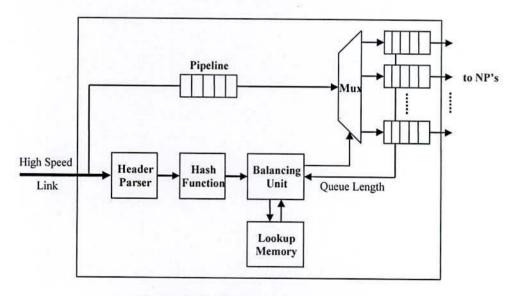

|             | 4.3.4 Load Balancing for High-Speed Links            | 41 |

|             | 4.3.5 Load Distribution Algorithm                    | 42 |

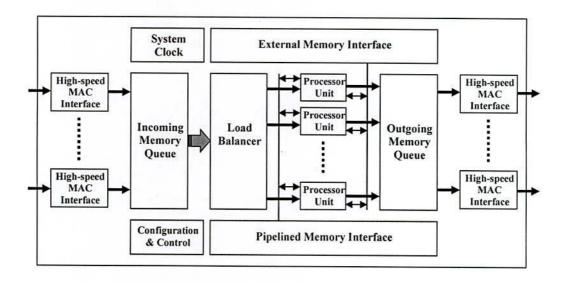

|             | 4.4 Proposed Architecture                            | 44 |

|             | 4.4.1 High-Speed Ethernet MAC                        | 45 |

|             | 4.4.2 Load Balancer                                  | 45 |

|             | 4.4.3 Processor Unit                                 | 46 |

|             | 4.4.4 Increasing the Throughput of Common Operations | 47 |

|             | 4.5 Overall Power Model                              | 47 |

| CHAPTER V   | Modeling and Simulation                              |    |

|             | 5.1 EZdesign Microcode Development Tools             | 50 |

|             | 5.1 Network Processor Simulator: NepSim              | 52 |

|             | 5.3 VHDL Modeling, Synthesis and Schematic Diagram   | 53 |

|             | 5.3.1 Working on Xilinx ISE Design Suite             | 53 |

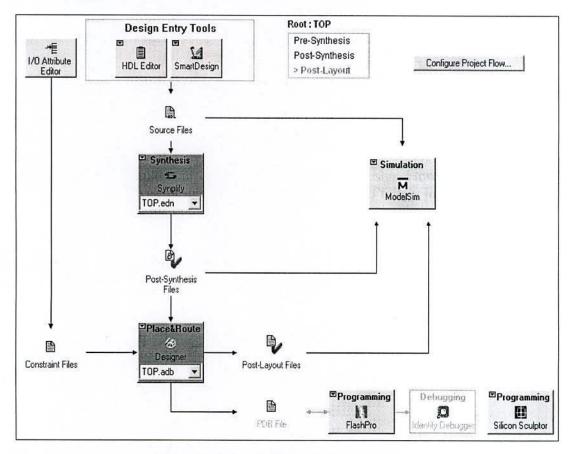

|             | 5.3.2 Working on Actel Libero IDE Design Flow        | 60 |

|             | 5.4 Simulation Waveform                              | 68 |

|             | 5.5 Synthesized Power Report                         | 70 |

| CHAPTER VI  | Performance Evaluation                               |    |

|             | 6.1 General NP Performance                           | 71 |

|             | 6.2 Architecture Analysis and Comparison             | 71 |

|             | 6.3 Evaluation Methodology                           | 73 |

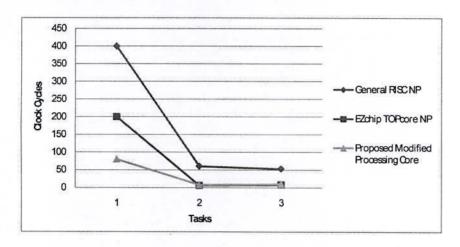

|             | 6.3.1 Real Packet Processing Operation               | 74 |

|             | 6.4 Summary                                          | 75 |

| CHAPTER VII | Conclusion and Future Work                           |    |

|             | 7.1 Conclusion                                       | 76 |

|             | 7.2 Future Work                                      | 76 |

| Deferer     | 2930                                                 | 77 |

# List of Tables

| Table |                                          | Page |

|-------|------------------------------------------|------|

| 3.1   | IP Address Example                       | 25   |

| 3.2   | Example of Routing Table                 | 26   |

| 3.3   | IPv4 and IPv6 Non-routable Addresses     | 27   |

| 4.1   | Cache capacitance for 0.35-µm technology | 49   |

| 6.1   | Comparison of packet processing tasks    | 74   |

# List of Figures

| Figure |                                                                                                        | Page |

|--------|--------------------------------------------------------------------------------------------------------|------|

| 2.1    | Software-Based Architecture                                                                            | 9    |

| 2.2    | Generic Network Processor                                                                              | 13   |

| 3.1    | ISO/OSI seven layers model                                                                             | 15   |

| 3.2    | TCP/IP model                                                                                           | 16   |

| 3.3    | Data (payload) encapsulation                                                                           | 17   |

| 3.4    | Network Model                                                                                          | 17   |

| 3.5    | Router layers                                                                                          | 18   |

| 3.6    | Internet Model                                                                                         | 18   |

| 3.7    | A general framework of packet processing                                                               | 20   |

| 3.8    | Ingress and Egress Processing Configuration                                                            | 20   |

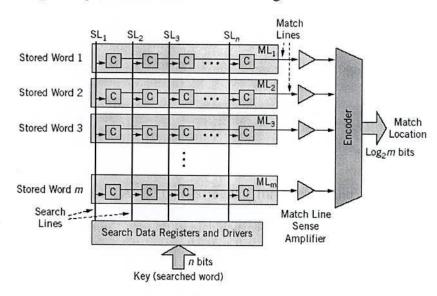

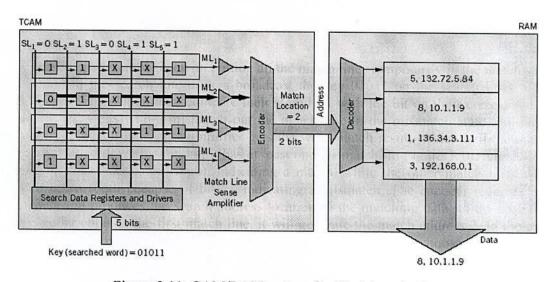

| 3.9    | Simplified CAM scheme                                                                                  | 29   |

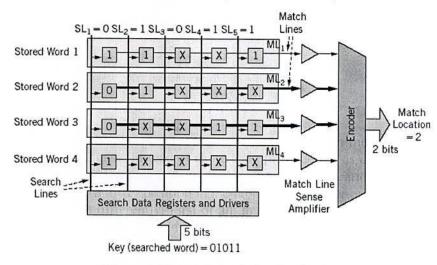

| 3.10   | TCAM priority mechanism                                                                                | 29   |

| 3.11   | CAM/RAM system for IP address lookup                                                                   | 30   |

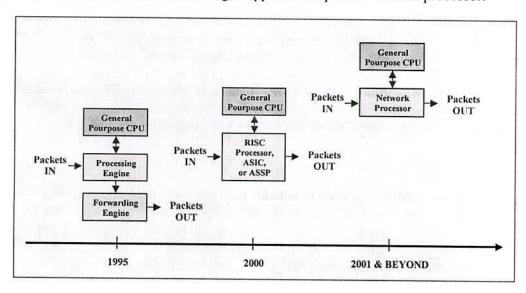

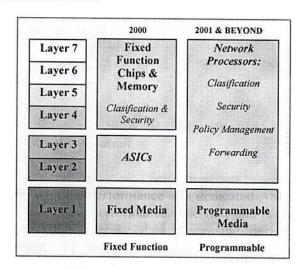

| 4.1    | Evolving the Network Design System Philosophy                                                          | 32   |

| 4.2    | Graphical comparison between network processor-based systems and their hardwired counterparts          | 33   |

| 4.3    | Embedded processor architecture in which a single processor handles all packets                        | 35   |

| 4.4    | Parallel architecture in which the incoming packet flow is divided among multiple processors           | 35   |

| 4.5    | Pipeline Architecture in Which Each Incoming Packet Flows Through<br>Multiple Stages of a Pipeline     | 36   |

| 4.6    | An example architecture that uses parallel pipelines of homogeneous processors (Cisco)                 | 36   |

| 4.7    | An example architecture that uses a pipeline of parallel stages with heterogeneous processors (EZchip) | 37   |

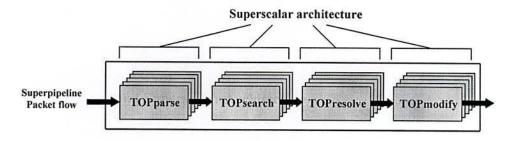

| 4.8    | EZchip TOPcore superpipeline and superscalar processor architecture                                    | 37   |

| 4.9    | Layered processing architecture                                                                        | 38   |

| 4.10   | Pipelined wide-word memory architecture                                                                | 40   |

| 4.11   | Load-balancer system                                                                                   | 41   |

| 4.12   | Diagram of Load-balancer                                                                               | 41   |

| 4.13   | Large flow accommodation through reassignments                                                         | 43   |

| 4.14   | Block diagram of proposed Network Processor                                                            | 45   |

| 4.15   | High-speed Ethernet MAC Interface                                                                      | 45   |

| 4.16   | Load balancer diagram                                                                                  | 46   |

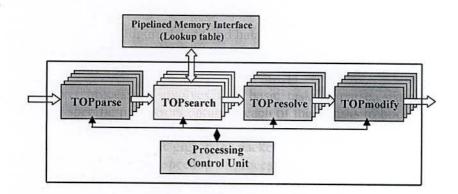

| 4.17   | Proposed modified architecture of processor unit                                                       | 46   |

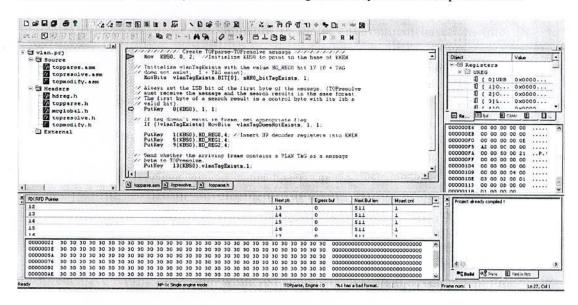

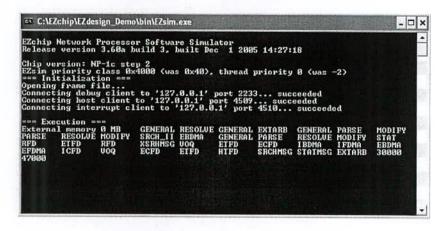

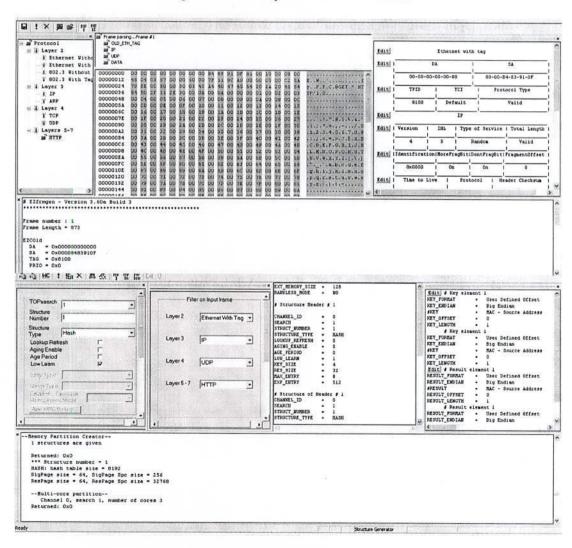

| 5.1    | EZchip microcode development environment                                                               | 50   |

| 5.2    | EZchip NP simulation status                                                                            | 51   |

| 5.3    | Generating Frame structure                                                                             | 51   |

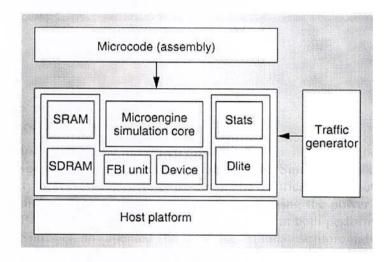

| 5.4    | NePSim software structure                                                                              | 52   |

| 5.5    | I/O pin layout of the top module                                                                       | 53   |

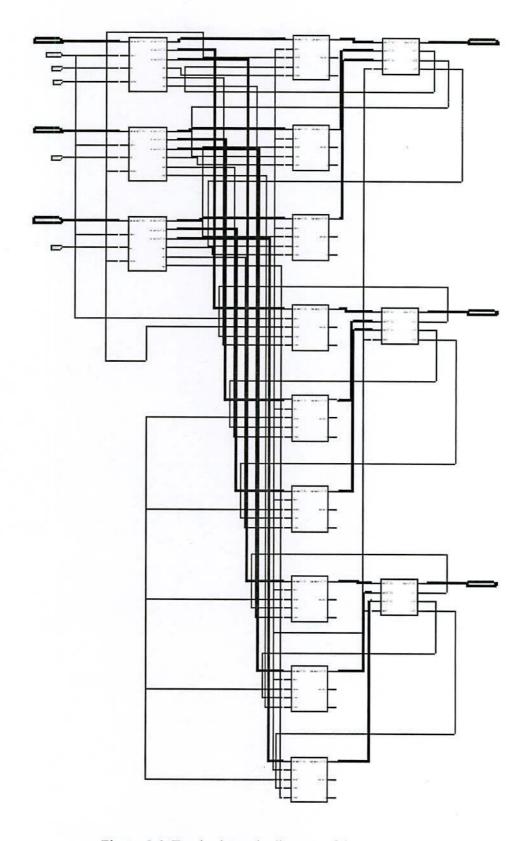

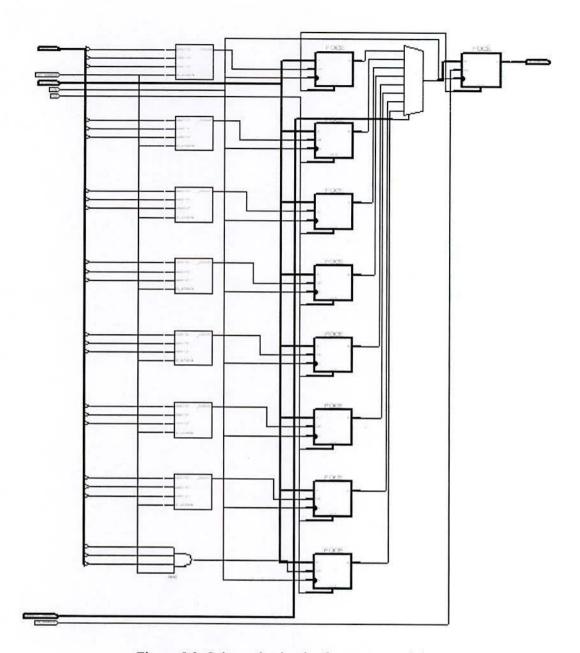

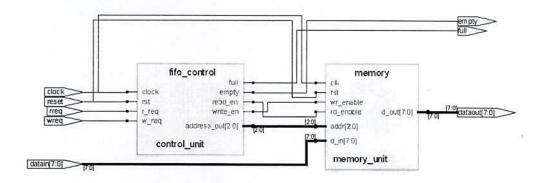

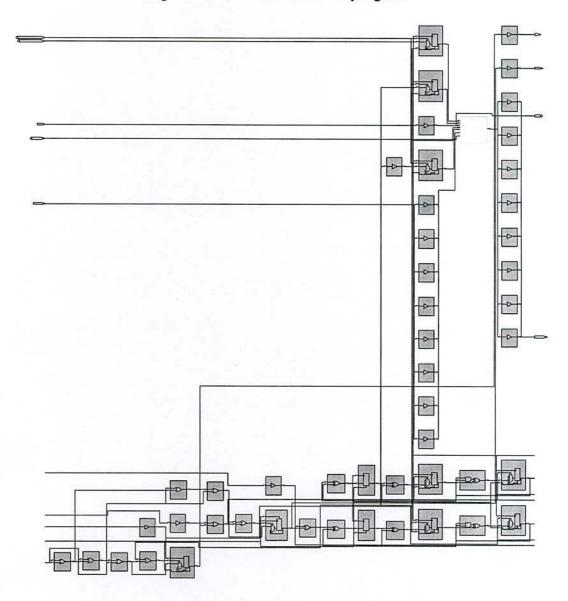

| 5.6    | Total schematic diagram of the top module                                                              | 54   |

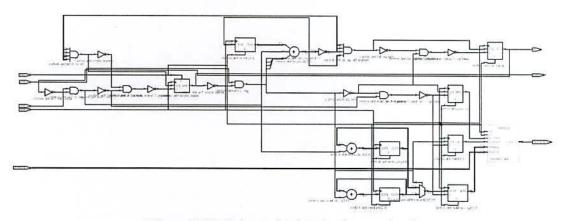

| 5.7    | Schematic circuit of control module                                                                    | 55   |

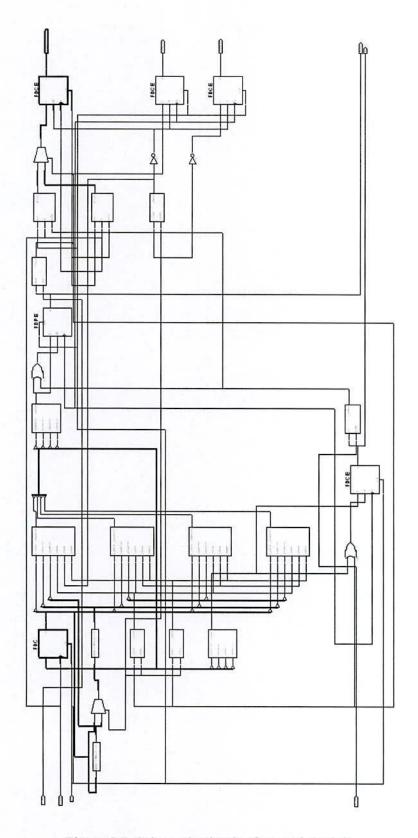

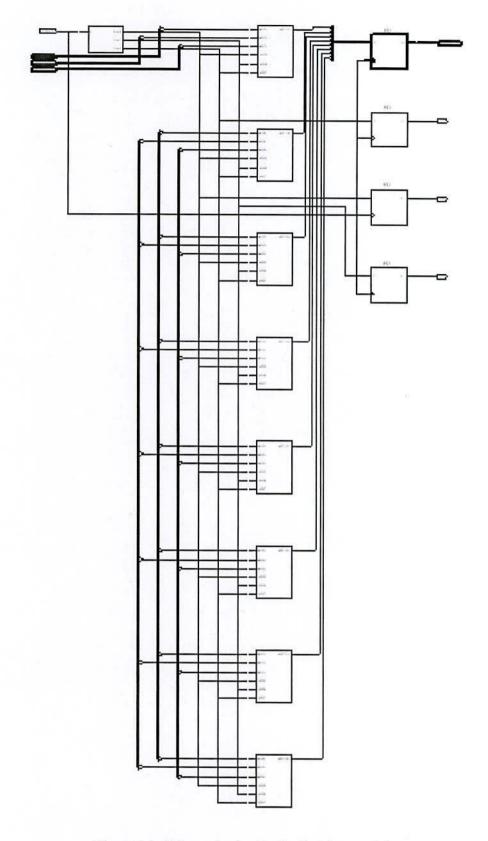

| 5.8    | Schematic circuit of scheduler module                                                                  | 56   |

| 5.9  | Schematic circuit of memory module                       | 57 |

|------|----------------------------------------------------------|----|

| 5.10 | Actel Libero IDE Design Flow                             | 60 |

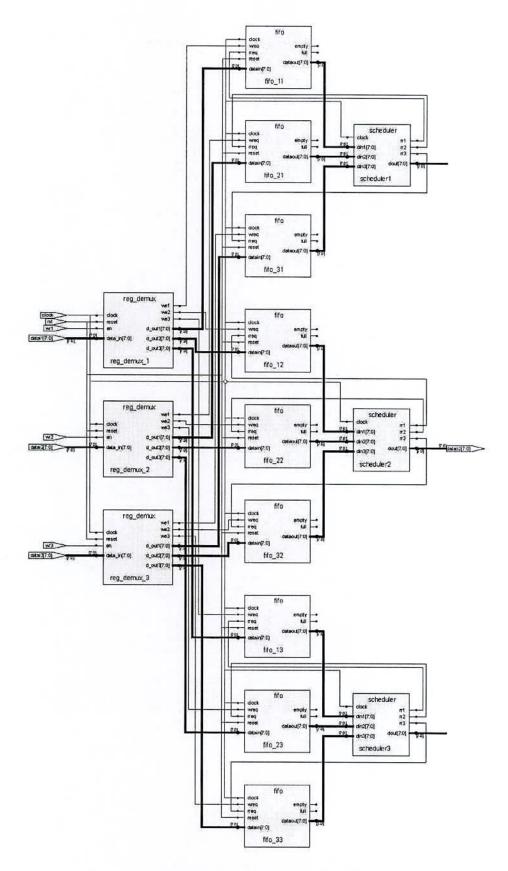

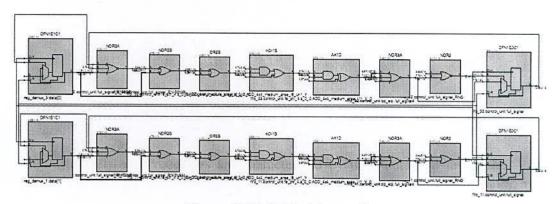

| 5.11 | RTL Synthesis block diagram                              | 61 |

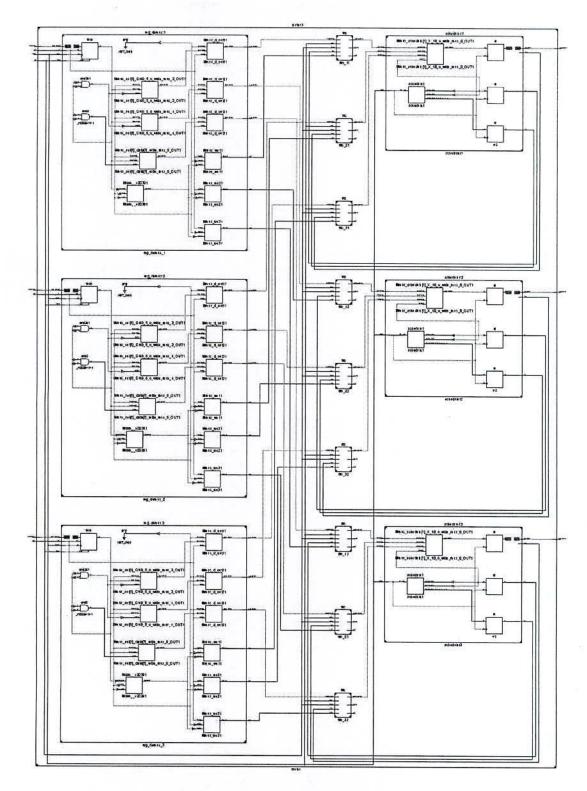

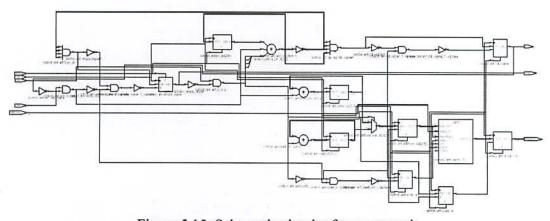

| 5.12 | Full synthesized schematic circuit                       | 62 |

| 5.13 | synthesized diagram of memory and control unit           | 63 |

| 5.14 | Schematic circuit of control unit                        | 63 |

| 5.15 | Schematic circuit of memory unit                         | 63 |

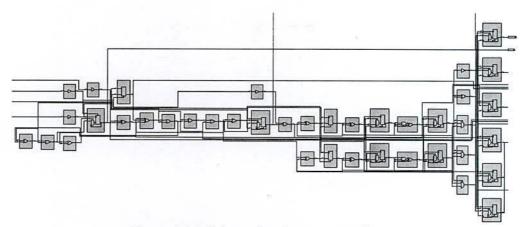

| 5.16 | Schematic of memory register                             | 64 |

| 5.17 | Data path diagram of control operation                   | 64 |

| 5.18 | Critical data path                                       | 65 |

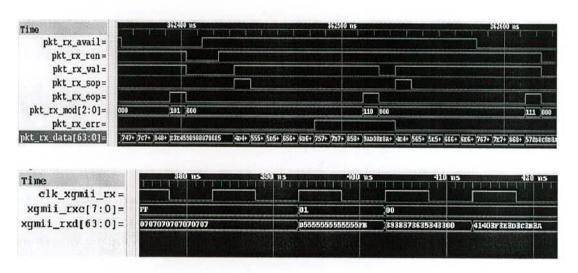

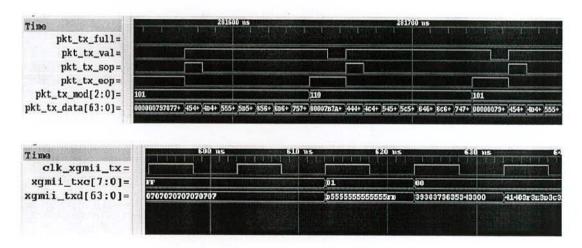

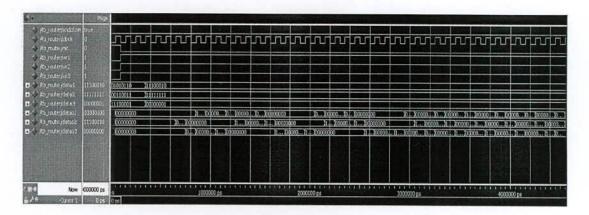

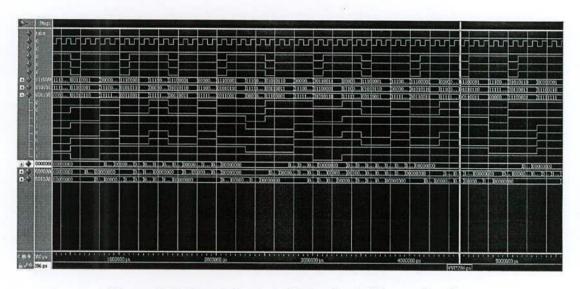

| 5.19 | Simulation waveforms of packet receive interface         | 68 |

| 5.20 | Simulation waveforms of packet transmit interface        | 68 |

| 5.21 | Simulation waveform of routing application               | 69 |

| 5.22 | Simulation waveform of switching application             | 69 |

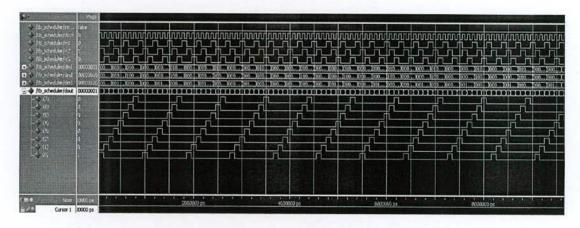

| 5.23 | Simulation waveform of Load scheduler                    | 69 |

| 6.1  | Block diagram of proposed Network Processor architecture | 72 |

| 6.2  | Proposed modified architecture of processor unit         | 72 |

| 6.3  | Performance comparison graph                             | 75 |

# **CHAPTER I**

# Introduction

The bandwidth requirement of communication network is increasing with the increases of various network applications. This rapidly increasing consumption of bandwidth significantly shapes the development of the transport networks and the communication terminals. Running high-speed networking functionalities on today's communication systems requires that a lot of functions are to be implemented in a hardwired manner. The ultimate throughput of communication systems depend on its network processing equipments. In recent years, fiber optic link technologies throughputs have expanded at greater rates and it increases the burden on the routing technology. With greater bandwidth and greater network processing requirements to handle traffic, it has become apparent that previous methods of traffic processing are unable to meet the current market requirements and high performance. This has brought about the development of one of the most promising technologies in this area, namely Network Processor (NP).

With the introducing of recent faster communication medium the total communication performance is not increased well with communication lines. The reason is the lagging of faster networking devices. In recent technology most often engineers are trying to use fiber-optic communication medium to speed up the network communication, but the conventional networking devices are not simultaneously speedy with the optical medium. As a result the total performance is depending on the processing element of the network devices. So, for getting high performance network operation it is needed to speed up the network processors, the main packet processing element of the networking device. Researchers are still trying to increase the speed of the network processor and for that they introduce many more methods and techniques regarding this.

#### 1.1 Background and Previous work

During past 20 years, engineering of network systems has changed a lot. Their architectures can be divided into three main generations: [1]

- The first generation goes back to 1980's when standard processors were used for network applications, e.g., like a minicomputer for routing.

- The second generation runs by mid of 1990's, speed and complexity of systems had gone up, so designers added special hardware blocks to relieve the load from CPU.

- The third generation systems employed very specialized hardware in ASIC (application specific integrated circuit) and even attempted to use several of them for higher performance systems. Because the protocols were consolidating around Ethernet and IP at those days, not much flexibility was needed and fully hardware fixed solutions were satisfactory.

As can be noted in the transition above, with each new generation the programmability of network devices were traded for higher speed through adding more hardwired components. Towards the end of 1990's, the Internet boom period, convergence of voice and data networks started to become more imminent. As a result, new and wider range of

protocols and services, e.g., multimedia services, needed to be developed by the industry. The pace of introduction of new services and their further upgrades had become faster shortening the product cycle and requiring faster time-to-market. Furthermore, more complex services were expected to become the norm, for example moving the routers beyond just store and forward machines and increasing the required processing power several order of magnitudes of the exiting level.

The best solution seemed to be bringing back programmability which was the hallmark of the first generation network but not at the cost of performance which was the hallmark of second generation network. The result was a new hardware known as network processor (NP) today. Network processors need to deliver the speed of silicon which is combined with the intelligence and flexibility of programmable microprocessors. The key to network processor success is an architecture that enables implementation of high-level applications in high-speed networking environments [3].

Owing to increasing network data rates and more sophisticated networking protocols, networking solutions continue to demand more powerful processing capabilities [7]. The processing of packets is the main job of the network systems [8]. Current packet processing device approaches designed for performance at multiple gigabit-per-second data rates and used network processors that are used in routers or switches. True Network Processors are usually large SoC (System-on-Chip) with multiple processing devices. These processing devices are usually very simple, specially designed generic processors [9]. True Network Processors can also be implemented using other techniques such as massive multithreading and usually include custom hardware for packet processing [10].

From the late 1999 the researches on network processing hardware for high speed communication is significantly growing up and still continue. Architecture for fast packet processing [14], slow response time, higher throughput, multithreading [9] on network processor, parallel processing [15], adaptive processing [11] approach, FPGAs [13] and ASIC implementations for high speed packet processing etc. is the major area of that research.

In April 2002, researchers at the University of Southern California's Information Sciences Institute demonstrated a first-generation giga-bit rate packet processing system implemented in several FPGAs [12]. The researchers sought to address the performance bottleneck imposed by the Central Processing Unit (CPU) in single-processor gigabit networking systems. Packet processing functions including basic routing, encryption, and framing are performed in the reconfigurable components. Three separate Xilinx Virtex XCV1000 FPGAs (X0, X1 and X2) are used to process data traffic [12].

In 2002, Gordon Brebner of the University of Endinburgh described a gigabit IP router [13] that fits on a single Xilinx Virtex-II Pro XC2VP7 FPGA device. This router takes advantage of the configurability of the FPGA to maintain system performance as traffic migrates from IPv4 to IPv6.

#### 1.2 Motivation and Objectives

Network systems, such as routers and switches, started as conventional central processing units. They have a CPU, RAM and ROM to store the operating system and interfaces to connect to the network. At the beginning, their performance was sufficient. With the rapid growth of the Internet and applications, they became a bottleneck. They could not reach

the required speed for packet throughput. To solve this bottleneck, ASIC was introduced. ASIC is an integrated circuit designed to perform the networking functions at wire speed. The networking functions are designed into silicon hardware permanently.

Bandwidth is important and critical to network applications. Because emerging Internet applications increase the network traffic, it is pushing the limit of the capacity of communication lines and semiconductor technologies. Therefore, network equipment providers are searching for better technologies and methods to handle, support and manage the traffic.

Currently, researchers are exploring several different approaches to high speed networking. Most of the work has concentrated in the areas of improving switching architectures [1]. Therefore, network equipment providers are searching for better technologies and methods to handle, support and manage the traffic [2]. Network processors present a solution, which can help maximize bandwidth utilization and traffic flow [3, 4]. And now it is the main component in the network systems to meet the new bandwidth, speed, and performance requirements.

From the study of this related works, it is found that network devices that use network processor are not speedy well with the communication medium. Moreover, researchers are still trying to increase the speed of the network processor. So, research on this area is the important issue to increase the network performance and meet the current networking demands.

Again due to higher bandwidth requirements and to support the real-time applications with high-speed communication medium (like: optical fiber), the main issue for improving the routing systems are to design such a network processor which considers the following:

- Increase processing speed and reduce mean system wait time

- · Faster time scheduling and memory queuing architecture

- Use adaptive methodology for support various packet processing

- · Parallel packet processing from multi queuing system

- Multi protocol supporting and multi-threading capability

- Parallel processing with multi-core processor unit

- · Programmable and scalable processing architecture

- Synchronous processing capability with different communication medium

The objective of this thesis work is to design such a network processor architecture that speeds up the packet processing power.

#### 1.3 Scope of the thesis

Network processing is an active field both academically and commercially. Network researchers are always try to speed up the processing power of a network processor to reach its incoming traffic speeds. Different methods and techniques are introduced by the different academic researchers. On the other side, commercial network processors are viewed as the next step towards high-speed data traffic processing and are currently enjoying a third generation systems. At the same time, academic research continues with new methods of providing network services in reconfigurable hardware.

### 1.4 Approaches

In the first step of this thesis work is to study on various network processors with their design architecture and functionality. Then study on the methods and algorithms that the existing processors used to achieve their specific purpose. From the study and analysis, this research finds some techniques and methodology for designing efficient network processor hardware. The Task Optimized Processing core (TOPcore) technology is chosen for designing the core processing unit. To processing in a parallel way pipelined architecture is developed with pipelined memory interface. An efficient load balancer is used for high performance parallel processing. The whole processes are followed by a hierarchical layered processing strategy.

Finally, the design will be modeled and simulated in RTL level using VHDL and then synthesized to a schematic. The design is also simulated in ModelSim Simulator and generates simulation waveforms.

# 1.5 Challenges

The performance aspects of network processor design continue to be challenging. Additionally, there are now other concerns of growing importance that focus on software and new applications for network processors. The design and application spaces are very large. Programmability remains a substantial challenge due to the different types of NP architectures, the evolution of networking standards and applications, and the unavailability of a unified and widely accepted set of software development and performance prediction tools.

On the other hand, with introduction of optical fibers in transport networks, the serial time-division multiplexing (TDM) synchronous optical network/synchronous digital hierarchy (SONET/SDH) transmission speed grew exponentially and reached 40 Gb/s rate by 2000 [2]. Though the speed increase was not expected to go beyond 100 Gb/s because of the limits of transceivers, this had already put pressure on the network device designers. To make the situation more challenging, deployment of WDM transmission technology brought radical changes increasing transmission capacity of fiber links to 1.6 Tb/s and beyond [2].

## 1.6 Organization of the thesis

This section reviews the topics covered in sequence and remainders organization of the whole thesis work.

- Chapter 2 describes the overview of the Network Processor (NP) systems. The

evaluation and generation, application and generic NP architecture are described

there.

- In chapter 3, data processing models and details packet processing functions are described.

- The chapter 4 is for the architectural definition of NP and describes the methodologies that are used in this thesis. The proposed architectural design and the proposed modified design of processor unit are given in detail there.

- The architectural microcode simulation, VHDL modeling and synthesized results are given in detail in chapter 5.

- The performance evaluation of the thesis is described in chapter 6.

- Chapter 7 gives the conclusion and future work of the thesis.

# **CHAPTER II**

# Network Processor Review

#### 2.1 Overview

Communication over the Internet is built on packet switching. The processing of packets is the main job of the network systems such as switches and routers [2]. These network systems examine each packet, and then decide what to do with them. Typically, this decision depends on the headers of the packets. They can be forwarded to interfaces of the system or returned to the sender as an error message. The functions and the services that the network system provides depend on the architecture of the network system processor.

A network processor, unlike the conventional computer processor unit (CPU), combines hardware functional units with software, and is designed and highly optimized to perform network functions [2-4]. For high bandwidth and performance, parallelism and pipelining are used in the design of Network Processors.

A Simple definition of a network processor is that it is a programmable device which is specially designed to process packet data at wire speed [7]. However, this definition doesn't really clarify what the Network Processor has to process. This is summarized in more detail below.

- 1. Pattern Matching: Here the network processor compares packet fields with specific patterns, to classify the type of packet, for example to decide whether a packet is an IPv4 or an IPv6 packet.

- 2. Lookup: Here the network processor takes a packet field and performs a lookup in a table to return the relevant table entry. This table may be either in internal memory or external memory. For small fields the table can be one-to-one and only require a single lookup. However, for larger fields, a tree search may be require to find the correct table entry, in this case multiple lookups may be require. A typical lookup may be to perform a lookup on the destination address to identify the IP address of the next hop.

- 3. Data Manipulation: This is where the packet is modified in some way. This could be decrementing the Time-To-Leave (TTL) field in an IP packet, recalculating the CRC check, performing packet segmentation and reassembly, or encryption/decryption of a packet.

- **4. Queue Management:** This is where the scheduling and storage of the packets is handled to provide traffic shaping and quality of service priority queuing.

Network processors vary in their level of:

- -programmability,

- -processing power,

- -extent and ease of configuration,

- -flexibility,

- -adaptability and

- -inclusion of specialized hardware structures [20]

Programmability is the ability of loading a program (set of instructions to perform a certain task) or a set of registers (setting the initial state of the processor), such as in Switch core NP. While the level of programmability may enable the support for a wider variety of applications, it also increases the level of complexity of product development (creating a program requires more work than setting a set of configuration registers).

Processing power is a measure of the data processing capacity, usually measured in millions of instruction per second (MIPS), millions of floating-point operations per second (MFLOPS), millions of bits per second (Mbps, megabits per sec.), millions of bytes per sec. (MBps, megabytes per sec.), millions of clock cycles per sec. (MHz megahertz), millions of packets per second (MPps). The units used differ between manufacturers, but most use a measurement of the throughput of data on the communication medium. These are measured either in 'Mbps' or in 'MPps'. 'Mbps' gives a good indication of the communication mediums that can be connected to the system, but does not give any indication of the amount processing that can be done on the packets. 'MPps' is a better indication of the amount of processing, but is highly dependent on the protocols and traffic patterns on the network. It requires information on the protocols, types of processing, and types of traffic. In the network processor market, the 'MPps' is by far the most favored unit of processing power. There is no perfect type of processing power measurement. The processing power of the Network Processor depends not only on the number and the speed of the core processor(s), and the amount of threads on each core, but also on their efficiency and specialized hardware structures. For example, both the MMC NP7120 and the Agere (Lucent) FPP/RSP support a line bandwidth of 2 x OC-48 (5 Gbps), but the Agere Network Processor has 1700 MIPS versus 440 MIPS for MMC's network processor. The Network Processor from Agere has 4 CPU cores versus 2 for the MMC and the Agere also has hardware support for a total of 64 threads versus 8 per CPU [21]. Multiprocessor and multithreaded systems increase the power of the Network Processor, but that requires the breaking of the algorithms into multiple parts. While networking naturally lends itself to parallelism, it can still be difficult to split the algorithms into the 64 threads that some of these Network Processors have and to balance the load over the 16 processors.

Extent and Ease of Reconfiguration is related to the programmability, as it is partly measured by the ease of re-programmability or reconfiguration, whether it can be done in the field, on the fly or if it requires removal from the system. It is also related to whether the network processor has any FPGA-like structures to allow the designer to load custom hardware structures into the design, as in the Chameleon CS2000 Family, and to the type of programmability (on the fly, etc...). This feature can increase overall throughput of the system by allowing for time-division-multiplexing, but will increase the latency of the Network Processor.

Flexibility is the ease with which the network processor can be configured or adapted to a given task, protocol or service. Flexibility is related to which functions can be implemented in software, which functions can be implemented in custom hardware and whether the interconnect between chip components can be reconfigured.

Adaptability is the ability of a chip to support different types of protocols, services, communication links and bus standards (PCI, AMBA, etc...). It is the ease with which it can adapt to the environment in which it is placed.

Inclusion of specialized hardware structures provides on-chip specialized packet processing structures that would normally be present in an ASIC design and usually delivering considerable performance enhancement for network specific tasks. Structures such as polynomial-based hashing hardware, SRAM read write queues, address lookup tables, parallel processing power and even integrated SRAM and SDRAM controllers are among the cores that can be included in a Network Processor. An example of such hardware structures integration is the IBM Power Network Processor. Such inclusion of specialized hardware structures provides performance enhancements and/or greater system integration.

#### 2.2 Evaluation

Over the last 20 years, network systems especially router architectures, have evolved through three generations, each marked by improvements in packet processing mechanisms.

# 2.2.1 First-Generation Systems

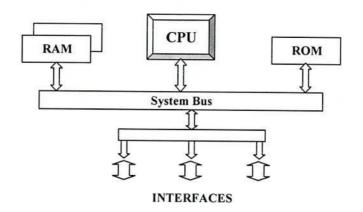

Up to the mid 1990's, router architecture was similar to the conventional PC systems. Figure 2.1 illustrates a CPU that performs networking functions, controlled by the router's operating system. Like conventional PCs, the router's operating system resides in the system's volatile memory in RAM and controls all the system's functions and services.

In such a system, all tasks are controlled and performed by software, and routers built in this system are called software-based routers. Because routing is software-based, adding new functions and services to the router can be done by simply changing or adding new instructions to the software [2-4].

It is good for the vendors because it does not take much time to change or upgrade the router's software. They could quickly develop new or special purpose products within a short time. The Cisco 2500 Router is an example of a software-based router (Figure 2.1). Cisco 2500 uses its Central Processor Unit to execute and conduct its routing instructions stored in nonvolatile RAM.

As Networking technology and applications changed, the drawback of this system became apparent. Software-based architectures had a limited ability to scale to higher bandwidth demands and new routing services [4]. For example, the majority of software based routers can only support wire speed throughput for less than 155 Mbps [4]. For perform complex networking functions, like filtering, policy based routing, and examining traffic statistics, the throughput of software-based routers is reduced. This creates a bottleneck in the network [4].

Networking technology was constantly developing, but software-based architecture could not keep up with the bandwidth demand and started to suffer in performance. In addition, maintaining this architecture became very expensive.

Figure 2.1: Software-Based Architecture.

# 2.2.2 Second-Generation Systems

After the mid 1990s, companies started to find new solutions to support high bandwidth and fast processing networking systems. Vendors used Application Specific Integrated Circuits (ASIC) and combined them with embedded Reduced Instruction Set Computer (RISC) processors yielding greater speed and performance. Companies that built high-speed network systems started to hire VLSI design engineers to design ASICs for their systems and products [2].

ASIC-based forwarding and switching have resulted in a new generation of very high-speed routers and switches. ASIC is an integrated circuit manufactured with embedded instructions to perform specific functions. The functions are programmed in silicon hardware permanently. So, for ASIC, since there is no memory instruction fetch cycle, it is significantly faster than software-based systems. It works at wire speed. That is, in the software-based architecture, the CPU must make memory accesses to execute instructions, and memory accesses take too much time compared with the execution time of ASICs.

With ASICs, manufacturers improved the performance by creating special chips that could do packet forwarding directly in the hardware. These chips make decisions about packet forwarding and, when packets need special treatment, they are forwarded to the RISC processor for special treatment. With very high packet forwarding speeds (approximately tens of millions of packets/second), routers became very inexpensive. They became common in academic and industrial networks [2, 4]. Now, one can buy sophisticated routers for \$100 or less.

ASIC technology became very popular because it can process packets at wire speed. But, after several years, its drawbacks started to be understood. ASICs are created by designing and fabricating networking functions into silicon permanently. In the meantime, Internet applications are becoming more complex. Thus, they need still more functionality. Some of those applications, such as Firewall Capability (stateful firewalls), Virtual Private Networks (VPN), and Quality of Service (QoS) implementation demand new processing capability from the network hardware [6].

To add a new function to an ASIC, we have to design and produce it from the beginning. This procedure takes from several months to two years. ASIC can be designed for several

different functions, but since those functions are embedded into silicon, adding new functions, or designing new ASICs are very expensive and time consuming [6].

To summarize, ASICs have numerous disadvantages: They are costly, require much time to market, and exhibit difficulties in simulation, design, and modification [2].

# 2.2.3 Third-Generation Systems

Network systems vendors can no longer afford to wait as long as two years designing and developing ASICs for an application. The network requirements could change during the development of a special purpose ASIC, and a lot of effort and money could be wasted [7]. The solution is Network Processors. Network Processors were introduced in the market in the late 1990s. Network Processors combine two approaches, hardware structure (about as fast as ASIC) and software that makes the system flexible.

Network processors are not for a special application. A vendor can produce different systems with different network functions with only one type of network processor. Today, designers can build a layer-3 unicast router; tomorrow designers can build a stateful firewall. Applications that are overwhelming for ASICs, because of the complex functionality, are implemented with network processors, such as Virtual Private Networks, firewalls, and Quality of Service mechanisms. These functions require more scalability, flexibility, and programmability.

# 2.3 Applications

The application of network processors is another area were abundant growth will take place. These processors will be targeted at "edge applications" and "backplane applications". Edge applications are where LAN and WAN protocol and packet translation frequently are required. Backplane applications are where a high concentration of source ports must each be forwarded to the appropriate destination port. Uses areas are Remote Access Servers, Web Switches, Internet Core Routers, Enterprise Routers and SOHO Intrusion Detection systems etc.

#### Remote Access Servers

These are servers that function as a large bank of modem to allow remote users to dial-in to access an enterprise network or the Internet. Recently, the access to the Internet through Internet Service Providers (ISP) has been as major focus of RAS. ISP's have customers wanting to do all kinds of different things. A RAS needs to be programmable to meet the needs but also faster and at a smaller cost per port. Current architectures have simplified line cards and a central switching point to route traffic. The line cards are inexpensive but this approach does not scale well. Traditional CPUs are designed based on locality of reference; they make the assumption that data recently referenced is likely to be referenced again in the near future. A cache helps make these systems run fast by keeping recently referenced information close to the processor. Thus the traditional CPU design bogs down in the face of constant streams of new data. A network processor takes a different approach. High-speed data movers collect data from network devices and move it directly to memory for queuing. While data is being moved to memory, it is selectively copied to special high speed engines that are able to parse the packet data, and make on the fly decisions about how to forward this data. However, as mentioned above in the [Table Lookup algorithms] section, network processors can benefit for specially designed memory cache to aid in the routing table computation to make decisions on how

to forward a given packet. Multiple high-speed engines allow the network processor to handle the many simultaneous threads of traffic flowing in a high-speed network. Sophisticated memory interfaces insure that the data can flow in and out of the processor's memory without creating a bottleneck.

#### Web Switch

Web Switches' are a new breed of network switch devices that help businesses and other content providers serve the needs of their clients. These switches delve deep into the network packets to determine not just what destination was intended, but also what application is being run, and what kind of transaction is being requested within the application. This information can then be used to make intelligent decisions about how to forward this traffic. The Web Switch needs to handle several different types of tasks. Packet handling from many connections must be processed at a fast rate. State information about each client connection is maintained so those subsequent packets for the session are forwarded to the appropriate server. Other network load and management processing is also done. This requires a device that is very flexible. Using network processors to build such a device because of their inherent nature of being programmable offers such flexibility.

#### Internet Core Routers

These routers serve as the backbone to the Internet. ATM technology dominates these routers now and is very fast and efficient for [Layer 2] switching. However, [Layer 3] and [4] forwarding is needed; this requires that the network packet must be investigated to make a more intelligent forwarding decision. A switch that can handle existing requirement, known new requirement and unknown future requirements is needed. A router built upon a network processor has the flexibility and performance necessary to succeed at such a task.

# **Enterprise Routers**

In similar regards to the requirements of the Internet Core Routers, enterprises need [Layer 3] and [4] switching but also want a substantial reduction year to year in the cost per port of network devices. A system based on a network processor because of its programmability and low parts count can attempt to satisfy the needs of enterprises.

## **SOHO Intrusion Detection systems**

Small Office Home Office (SOHO) network device could benefit from using a network processor in a device that not only connect the client to the Internet but also does intrusion detection. Most SOHO's can not afford high priced network equipment or technical staff to protect against intrusions. A system that was programmable and relatively inexpensive with a long life span would be ideal in this situation. Because intrusion techniques are constantly changing, a network processor and its inherent programmability point to an ideal match of problem and solution.

### **Intelligent Processing**

Because the architecture incorporates flexibility by being programmable other areas of future direction will involve intelligent processing. This will take the form of system based on a network processor to be able to provide customers with features such as Quality of Service (QoS), IP billing, security and monitoring, and IPv6 to name a few.

# Quality of Service (QoS)

This feature is to ensure that a defined level of service is provided for network traffic. Most prominently this is in terms of a constant data rate; so important in audio and video data transmissions. To accomplish this intelligent processing must be done in the network devices. Currently this would have to be defined is silicon (ASIC's) and therefore, not easily changed. With network processor doing the intelligent processing, the programming can be changed to meet specific needs.

## **IP Billing**

Currently, all packets travel at "bulk rate" because routers cannot tell them apart. Routers that can analyze headers more thoroughly without compromising wire speeds will allow network operators to sort packets into digital equivalents of priority mail, first class, second class, etc... For example, in return for higher fees, the encrypted traffic on a corporation's virtual private network (VPN) could get a higher priority on an Internet backbone than the idle gossip in an AOL chat room. Such processing must be done without compromising wire speeds - and hence, the network processors.

### Security and Monitoring

Another application of intelligent processing is to investigate packets in order to monitor their behavior and to detect security violations. This requires a delving into the packets to examine the contained information. By processing this information intelligent decisions related to security and monitoring can be made. This is made possible with the programmability and wire-speed performance of network processor based systems.

#### IPv6

The next revision of the Internet Packet (IP) protocol is called IPv6. This revision will incorporate many new features into the protocol; the most notable is the address range of IP addresses. The source and destination addresses will 64 bits instead of the current 32 bits. Network devices that are not programmable will have to be replaced to take full advantage of the features in IPv6. With systems built upon a network processor the devices do not have to be replaced, only the software that controls them.

#### 2.4 Generic Architecture

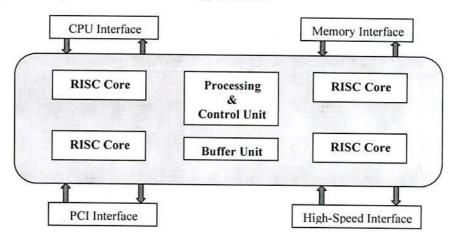

Network processor architectures make CPU architectures look staid and boring [31]. Figure 2.2 is a block diagram of a generic network processor. It does not represent a specific network processor, but includes traits common to most. These traits are:

- Multiple RISC cores

- Dedicated hardware for common networking operations

- High-speed memory interface(s)

- High-speed I/O interfaces

- Interface to general purpose CPU

Compared to general purpose processors, network processors do not need very sophisticated arithmetic and caching capabilities. Instead, they usually contain multiple execution threads running in parallel. Also specialized hardware units provide added functionality depending on the mainstream applications the network processor is targeted for. Packet processing is different from other applications intended for regular CPU in several ways [23]:

- It is I/O centric rather than process-centric.

- It has to be handled in real-time fashion.

- · It consists of many simple tasks instead of few big tasks.

- It keeps states per flow instead of per application.

- It requires atomic access to shared data as it is more geared towards parallel processing than the usual CPU applications.

Figure 2.2: Generic Network Processor

#### **Dedicated Hardware**

Network processors, particularly RISC based ones; provide specialized hardware or integrated co-processor to perform common networking tasks. Typical hardware functionality includes Lookup Engines, Queue management, CRC calculation and Encryption Functions. In some Instance this additional hardware functionality may be targeted specifically for a particular application and would be of no use in a different application.

#### **Network Interface**

A key feature of Network processors is their network interfaces. This is where the data packets enter and exit the network processor. These interfaces connect to the Framer or MAC device of the line interface. (Although some network processors have integrated framers and MACs, in which case the network processor connects directly to the PHY). Some of the early network processor manufacturers developed their own network interface, which means designing new framers with this interface or providing a bridge chip. Now, however most network processors implement standard interface to the Framers and MACs, such as UTOPIA level 2 and 3, SPI-3 and for 10Gbps traffic SPI4.2.

#### Switch Fabric Interface

Many of the high-end network processors are targeted towards routing applications and provide an interface to a switch fabric. In general the switch fabric interfaces comply with a standard switch interface such as CSIX or may be SPI4.2.

#### Control Processing

The main function of the network processor is to process packet data at wire-speed. Certain packets known as control and management packets do not need to be processed at

wire-speed. These include exception packets and table updates. These packets in general have more complex processing requirements than the data packets, which are processed by the PPEs, would slow down the packet throughput. These packets are therefore separated out of the main data path and passed onto a separate processor known as the control processor. This processor may also be responsible other functions such as statistics gathering. A general-purpose processor normally implements the functionality of the control processing. Many network processors contain an integrate core specifically for control processing. Alternatively the control processing functionality will need to be provided externally via a host interface, such as a PCI bus, to a general-purpose processor.

### Memory

Network processors require memory to store program code, lookup tables, packet data and queue information. Where feasible this memory is provided internal to the network processor. However, inevitable external memory will be required for many applications.

Most network processors will have at least two external memory interfaces, one to SRAM (Static Random Access Memory) and one to DRAM (Dynamic Random Access Memory). Accessing the external memory can cause a bottleneck; so many manufacturers are looking to the technologies to provide faster memory accesses, such as using DDR (Double Data Rate) or QDR (Quadruple Data Rate) SRAM, DDR SDRAM (Synchronous DRAM), FCRAM (Fast Cycle RAM) or RDRAM (Rambus DRAM). Packet data is typically requires large buffer storage, so in general it is stored in DRAM. Queuing information will usually be stored in SRAM.

The location of lookup tables depends on the size of the lookup table. large tables will need to be stored in DRAM, whereas smaller tables can be stored in SRAM or internally. Some network processors provide interface to CAMs (Content Addressable Memory), which allow very fast lookups. However, CAMs are still fairly small and so will limit the number of entries in the lookup table.

# **CHAPTER III**

# Data Networking and Packet Processing

## 3.1 Data Networking Models

Network modeling can be done in any one of the following two ways: either by modeling the data and the communications' protocols between the communicators, or by modeling the physical components of the network and their interconnections. Eventually, the two models converge into one representation of network modeling.

As data communications and telecommunications programming, interfaces, and equipment grew more sophisticated, the International Standard Organization (ISO) suggested a structured, layered architecture of networking called Open System Interconnect (ISO/OSI). At about the same time, the U.S. Department of Defense (DoD) offered another layered model that concentrated on data-network modeling (often called the Internet model, or more commonly, the TCP/IP model). These two models provide fundamental concepts in communications, and most systems and definitions use their language.

#### 3.1.1 ISO/OSI Model

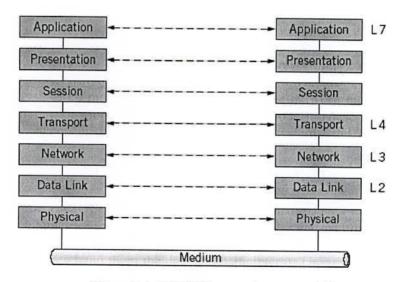

According to the ISO/OSI model, which is also called the seven-layer model, any two peered layers interact logically, carrying the relevant data and parameters, and executing the functionality of that layer. These layers actually interface with the layers above or below them (i.e., they hand them the data and parameters). The seven layers are shown in Figure 3.1.

Figure 3.1: ISO/OSI seven layers model

The physical layer handles bits and the physical transmission of bits across the communication channel through some sort of medium (whether it be a kind of wire, fiber, radio-waves or light). The second layer (referred to as L2) is the datalink layer, which takes care of framing bytes or a block of bytes, and handles the integrity and error

recovery of the data transmitted at this level between two nodes connected by a physical channel. The third layer (referred to as L3) is the network layer, which is responsible for carrying blocks of data between two or more nodes across a network that is composed of multiple nodes and data-links; L3 responsibilities include the required addressing, routing, and so on. The transport layer is the lowest application (or host) layer that carries data between applications (or hosts), independently and regardless of the networks used. It is responsible for the end-to-end data integrity and reliability, and it works through either connection or connectionless transport mechanisms. The session layer controls the session (e.g., determining whether the relationship between the nodes is peered or master/slave; establishing, maintaining, and terminating a session). The presentation layer determines such things as the format, encryption, compression, structure, and encoding of the application data. The application layer determines the way the application uses the communication facilities, that is, e-mail, file transfer, and so on.

The upper four layers (the transport, session, presentation, and application) are considered the host layers, while the lower three (the physical, data-link, and network) are the network layers. The network layers are considered the most important in network processing; nevertheless, many networking decisions are made based on the upper four layers, such as priority, routing, addressing, and so on.

### 3.1.2 TCP/IP Model

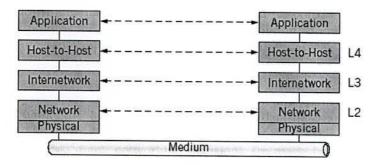

The equivalent data-networking model of the DoD (often called the Internet model, or more commonly, the TCP/IP model), is simpler, and contains fewer layers. (It originally had only four layers, without the physical layer; see Figure 3.2)

Figure 3.2: TCP/IP model

The ISO/OSI model layers are not mapped exactly onto the TCP/IP model layers; however, roughly speaking, the TCP/IP model shrinks all host layers into the host-to-host (transport) layer (L4), and adds a new, internetworking layer that is composed mainly of the ISO/OSI network layer (L3). TCP/IP's network layer (L2) is composed mainly of the functionalities of ISO/OSI's data link layer and some of its network layer. Recently, this model has been amended by a "half" (or a "shim") layer as new technologies have been introduced, so this model can better fit systems more precisely.

#### 3.1.3 Data Networking

The way the applications and other entities are multiplexed in one host and demultiplexed in the target hosts is by using headers in each layer, and data encapsulation. In ISO/OSI and TCP/IP models, each layer's entity interfaces with the entities in the layer underneath

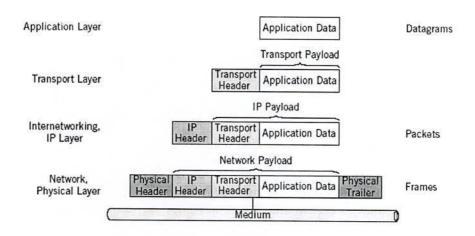

it by adding a layer-header describing the parameters required for the entity in the layer underneath to function properly. This header also lets the peered entity in the same layer in the other host to have the required information about how to process the data (according to the protocol). These headers are added as the data travels downwards through the layers, and they are removed as the data travels upwards. Figure 3.3 depicts data encapsulation in the TCP/IP model, and names the data units (Protocol Data Units, PDUs) that result; that is, datagrams in the application layer, packets in the IP layer, and frames in the physical layer.

Figure 3.3: Data (payload) encapsulation

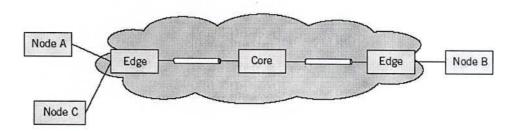

The other network modeling emphasizes the physical components of the network, and is composed basically of nodes and links. Some of the nodes are hosts or end systems (clients and servers, or peer communicators), and some are network edge devices or network core devices, as shown in Figure 3.4. Edge and core devices are gateways, routers, switches, bridges, hubs, and repeaters.

Node: Host PC, Server

Edge/Core: gateways, routers, switches, bridges

Figure 3.4: Network Model

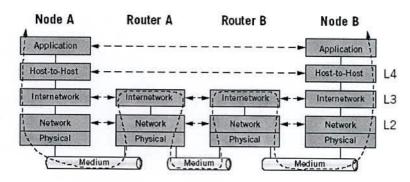

Network devices work up to the third layer (with the exception of gateways that work on all layers, and connect very different types of networks and applications). Generally speaking, repeaters and hubs work only on the first, physical layer, bridges, and switches work on the second layer, and routers work on the third layer. Thus, for example, routers interconnect networks and links by analyzing and forwarding packets based on the

headers of the third layer, as shown in Figure 3.5, where node A and router A are connected by one link (the left medium), and node B and router B are connected by another link (the right medium). The routers are connected by a third link (the middle medium).

Figure 3.5: Router layers

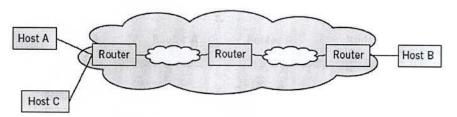

Links can be replaced, or generalized, by networks, such that, for example, the routers are connected by networks in between them, as shown in the Internet model in Figure 3.6.

Figure 3.6: Internet Model

#### 3.2 Packet Processing

Network processors are sometimes distinguished from packet processors by being programmable, whereas packet processors are just configurable. The programming paradigms, models, styles, and languages that are used for NPs are also very different from those used for applications running on general purpose processors. No interrupts are used in NPs, and the main principle is to use an event-driven control program, in which packets dictate how the software runs. Network processors perform several key functions, including:

- Parsing the incoming frames in order to understand what they are, and where to find the relevant information that is required for processing.

- Retrieving the relevant information from the frames, which may be complicated as

encapsulation, variable fields length, and various levels of protocols may be

involved.

- Deep packet analysis when required, such as understanding HTTP names, identification of XML protocols, and so on. This may be required for priority assignments for various kinds of traffic flows.

- Searching for related information in repositories; for example, routing tables, access lists, and so on.

- Classifying the frames according to the various forwarding and processing schemes that the frames should undergo.

- Modifying the frame's contents or headers, possibly adding tags, changing addresses, or altering the contents.

- Forwarding, which may potentially be coupled with various traffic management tasks such as metering, policing, shaping, queuing, scheduling, and statistics.

Packet processing tasks (or functions) include:

- · Framing.

- · Parsing and classification.

- · Search, lookup, and forwarding.

- Modification.

- · Compression and encryption.

- · Queuing and traffic management (measurement, policing and shaping).

Packet processing can follow one of two paths:

- Data path (fast path).

- Control path (slow path).

Packet processing can be discussed according to direction:

- Ingress (entering the equipment or the network processor, from the network).

- Egress (exiting the equipment or the network processor, to the network).

- · Combinations of Ingress and Egress.

# 3.2.1 Packet Processing Flow

Processing functions are separate tasks, each following the other. The process starts with the packet entering the network processor and immediately goes through framing, whose function is to make sure that the packet arrived correctly. (In the other direction, framing is the last task, and is targeted to ensure valid packet output.) The second phase is to parse and classify the packet, which simply means that the network processor must understand what the packet is, what type it is, and then must classify it according to the application requirements. Usually for this classification function, searching is required. The last function that the network processor carries is the required modification of the packet, which includes dropping the packet if required, multiplying it, or altering its content as required. Finally, transmitting the packet usually involves an extra function of queuing, prioritization, and traffic management of the packet to make sure that the receiver can receive the transmitted packet at traffic patterns that it expects. Queuing and traffic management sometimes happens inside the network processors and sometimes happens outside the network processors. Optionally, compression and encryption tasks are utilities that packets sometimes undergo and usually they are done outside of the network processor, although there are some network processors that contain an embedded security functional unit.

The main processing functions are classification of the packet (at real time or at wire speed), and searching for various values (e.g., next hop address) that correspond with some fields in the packets (e.g., IP address). These two functions have received extensive treatment in the industry, to the extent of special purpose search engine coprocessors, and the development of parsing and classification languages.

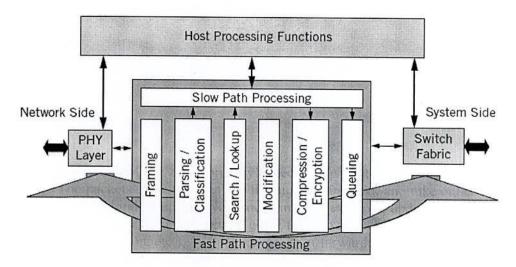

A general framework of the three primary aspects of packet processing is depicted in Figure 3.7. The packets enter from left, in the ingress direction, and take either the slow path (through some kind of upper level processing, for example, updating routing tables of the network processor), or the fast path (going through the network processor functions of searching, modification, etc.). The packets are then forwarded either to a switch fabric or to the network (line interface) again, in the egress direction.

Figure 3.7: A general framework of packet processing

# 3.2.2 Ingress and Egress

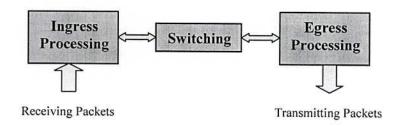

The packet processing flow is divided into three stages: ingress, switching and egress. The ingress stage is responsible of receiving packets arriving into the system. The switching stage is responsible for the transfer of packets from packet processing units on the ingress to packet processing units on the egress. The egress stage is responsible of transmitting packets exiting the system, See Figure 3.8.

Figure 3.8: Ingress and Egress Processing Configuration

In the Ingress configuration, the processing performed in the ingress queue includes such operations as checksum calculation, TTL updating, destinations address swapping and address lookup. After all the required processing operations are performed, packets are transferred to the Packet Buffering Unit, through the switch matrix. The Packet Buffering Unit places the packet on the output queues.

In the Egress Processing Configuration, the only information extracted from the packet on the input queue is the destination address. The information is used to determine the destination port and the packet is transferred to a Protocol Processor on the output queue through the switch matrix. Any needed processing is then performed on the assigned Buffer Processor on the output queue.

### 3.2.3 Framing

Received or transmitted frames should receive "framing" treatment, in order to assure that the correct and full packets or datagrams can be extracted from these frames. This means that incoming frames should undergo correctness tests (to make sure that the entire frames' bits are received without error), correcting attempts if required and integrity checks (to make sure that all packets' content arrived). Outgoing packets should be fragmented or segmented as required and "framed" correctly, that is, adequate headers should be attached or altered, proper terminators (trailers) should be appended or modified, and error detection and correction information should be added.

# 3.2.4 Parsing and Classification

After a complete valid packet is received and verified, the next step of packet processing is to look at the incoming packets in order to classify them for various treatments, as the processing requirements dictate. This step involves two combined subtasks: parsing and classification. Packet processing has two basic architectures, or design philosophies, that are crucial for parsing and classification implementation; these architectures are store-and-forward and cut-through.

In store-and-forward architecture, packets are first received in their entirety, stored temporarily, examined, analyzed, processed, and then, after a decision is made regarding them, transmitted, and the memory is cleared. Store-and-forward allows a complete, even complex treatment of the packet, before the packet is injected back into the network. This comes, however, at the expense of having to deal with buffering issues and delaying the packet, that is, adding end-to-end delay to the packet flowing from the ingress of the processing unit to its egress, due to the increased latency incurred by the buffering time that is required before processing starts.

The shortcomings of the store-and-forward are remedied by the cut-through architecture, where processing begins as packets flow into the processing units, and continues as bits continue to come in. The packet is transmitted after the required analysis, and the decision and processing is done "on-the-fly." This can be accomplished by examining specific bit patterns in various fields of the incoming packet, that is, parsing and classifying, as well as other decision and processing tasks that must be carried out in real-time. Although cut-through saves buffering and latencies, it allows only simple analysis, decision and processing tasks, and might even cause network overhead (e.g., transmitting a packet that eventually turned out to be invalid, bad CRC, or, because a premature decision was made based on the first bits of the packet, the output-channels were loaded in vain, forcing packet retransmits).

Examples of these two architectures are, on the one hand, in low-end routers that use store-and-forward architecture (no "wire-speed" constraints), and on the other, VLAN or MPLS switches that use cut-through architecture, based on a tag in the beginning of the

frame that allows forwarding decisions to be made instantly, while the packet is still inflowing.

# Parsing

Each incoming packet must go through some sort of parsing to examine and understand what it is as well as its requirements, and then it must be classified, or handled according to its type and its required processing. Parsing therefore is the first analysis and action done on the packet content. Parsing is basically identifying the relevant fields in the incoming packets, according to their place and type, and picking the field's values for continuing the parsing process, or using these values for classification. Therefore, parsing and classification are tied together and sometimes are not separated. A simple parsing example in an IPv4 packet would be to detect its destination IP address.

#### Classification

Classification means categorizing packets into "flows," in which they are processed in a similar way by the network entities. These flows are defined by rules that the packets obey, and the collections of these rules are called classifiers. The rule database contains many entries, each of which is composed of a pair of a specific rule description and its appropriate action. These specific rules are matched with the incoming packets, and the best match determines the appropriate action to be taken on the incoming packet. Very often, the action is to mark the incoming packet with a notation, so that a subsequent process will take the appropriate action, based on this notation.

A specific case of packet classification is packet forwarding, which deals with searching and packet lookups. In packet forwarding the rules are represented by the packet destination address fields, and the action is simply to forward the packet to its appropriate destination. In traffic management literature, classification is sometimes considered part of the traffic management process, when it classifies packets solely for traffic management purposes.

### 3.2.5 IP Lookup and Forwarding

The importance of rapid IP lookup cannot be exaggerated in the context of packet processing. The most common IP lookups are done for forwarding. IP packet forwarding is executed in any router or switch, where forwarding decisions have to be made in order to find the address of the next hop router and the egress port to be used to send the packet through. In most cases, IP forwarding is based on IP addresses. IP address lookups are obviously based on the IP address, that is 32-bit or 128-bit keys (IPv4 or IPv6, respectively), whereas other lookups can have much wider keys that can reach hundreds of bits, composed from multiple fields in the IP (or layer 2) packet.

Almost every packet processing activity starts with an IP-lookup, and therefore, in high-speed networks, the speed of IP-lookups is critical. Huge efforts are made to accelerate this specific task in any network processor or, as a matter of fact, in any networking device. In a 10 Gbps network, for example, the required time to forward a packet of minimal size is <50 ns; therefore, this is the maximum allowed time for looking for a match (or a longest match) of a specific IP address in a table of hundreds of thousands of entries (as well as doing some other things in this time frame).

#### 3.2.6 Modification

In all applications other than packet forwarding, modification of the packets is eventually the purpose of packet processing. Sometimes, some packet modification is required even for forwarding applications. For example, changing the IP header may be required in the time-to-live (TTL) field, as well in the IP addresses, hence recalculation of the checksum header is also required, and so on.

Packet modification can include all of these operations:

- Modification—Changing the contents of a packet (usually changes in its header, or changes both in the header and in the payload, as a result of some processing, e.g., compression or encryption described in the next section)

- Deletion—Some of the packet contents or headers are deleted (e.g. deencapsulation of packets)

- Adding—Additional information is added to the packet (e.g., encapsulation, authentication information)

- Canceling the entire packet—Simply removing the packet from the system (e.g., exceeded traffic, wrong addressing)

- Duplicating the packet—Copying the entire packet (e.g., multicasting, port-copy operations)

Since checksum is often changed in packet processing, some network processors contain an internal checksum functional unit to assist with maintaining the right checksums.

In addition, traffic analysis, some management tasks and other applications can be performed in the modification phase, although most of these operations are expected to be performed in the control path. Statistics collection, however, must be done in the fast path, at the modification phase, to accommodate the packet rate.

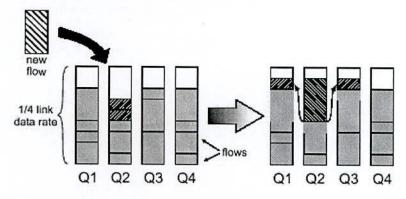

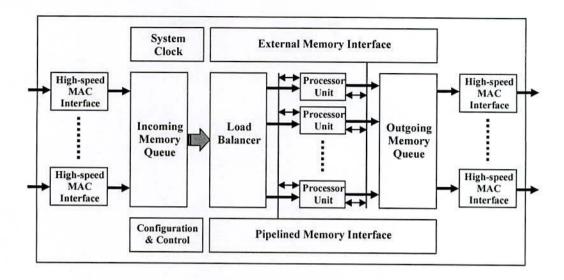

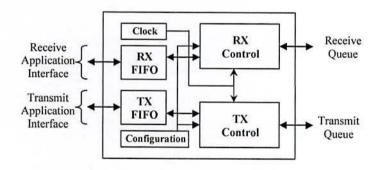

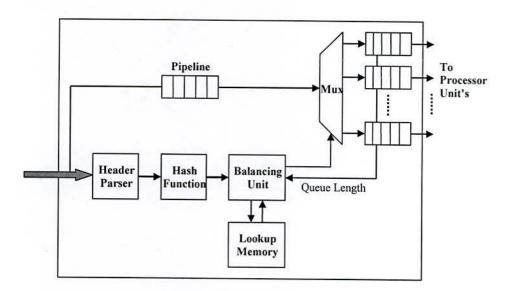

#### 3.2.7 Compression and Encryption