# Khulna University of Engineering & Technology B. Sc. Engineering Special Backlog Examination 2018 Department of Electrical and Electronic Engineering

#### EE 3113

### Digital Electronics and Logic Design

Time: 3 hours

Full Marks: 210

(09)

(07)

(06)

N.B.: (i) Answer **ANY THREE** questions from each section in separate scripts. (ii) Figures in the right margin indicate full marks.

### Section A

Q1. (a) Write down the significance of using complement's in digital system. Determine the (08) base and missing number "\*" for the following subtraction.

$$(5162 - 2644) = 2*15$$

- (b) Represent the number 3113)<sub>10</sub> in the following codes, (i) BCD, (ii) 2421, (iii) Excess-3. (06)

- (c) Explain the minimization technique using Quine-Mcclusky method. Determine the prime (12) implicants for the following function:

F (A, B, C, D, E) =

$$\sum (0,2,5,8,26,30) + \sum_{d} (10,12,24)$$

- (d) What are the performance indices of digital IC's? Explain them clearly.

- Q2. (a) Mention the differences between MUX and encoder. Implement the function, (10)  $F(A, B, C, D) = \prod(0, 5, 6, 8, 13, 14)$  using MUX.

- (b) Implement, F = AB + CD + E using NAND gate only.

- (c) Let  $f = \sum (5,6,13)$  and  $f_1 = \prod (4,7,12,14,15)$ . Determine  $f_2$  such that  $f = f_1 f'_2$ . (09)

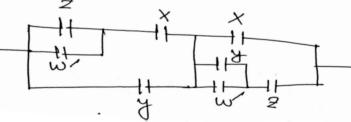

- (d) Express the following switching circuit in binary logic notation. Also implement by (09) NOR gate using b

#### Figure for Q2(d)

- Q3. (a) What is meant by ROM? Draw the logic construction of a 32×4 ROM. Design a BCD to (14) Excess-3 code converter circuit using ROM.

- (b) What is meant by PLD? Show the comparison among PLA, PROM and PAL. Implement (15) the following functions using PAL.

$W(A, B, C, D) = \sum (0, 2, 6, 7, 8, 9, 12, 13)$

- $X(A, B, C, D) = \sum (0, 2, 6, 7, 8, 9, 12, 13, 14)$

- $Y(A, B, C, D) = \sum (2,3,8,9,10,12,13)$

- $Z(A, B, C, D) = \sum (1,3,4,6,9,12,13,14,15)$

- (c) How can the fan out of DTL gate be increased?

- Q4. (a) Express  $F(A, B, C, D) = B + \overline{C}$  in POS form and also implement the function using (12) ROM.

- (b) What are the differences between ROM, PAL and PLA? Implement the following (12) function using PLA.

$F_1(A, B, C) = \prod (0, 1, 3, 5)$  and  $F_2(A, B, C) = \prod (0, 3, 4, 5)$

(c) Explain the significance of using parity bit in digital system. Design an odd parity (11) checker circuit for 3-bit system.

## **Section B**

- What is latch? What are the features of edge triggering flip flop? Q5. (08)(a)

- How can you use a T-FF as a pulse frequency divider? How can a chain of T-FF be used (b) (09)as counter?

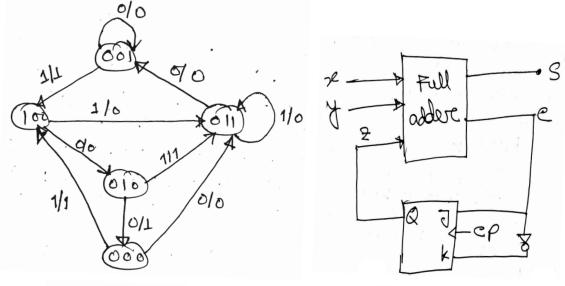

- Design a sequential circuit that has 3 FFs A, B and C, one input x and one output y. The (c) (12)circuit is to be designed by treating the unused states as don't care conditions. Use JK  $F^{F_{c}}$  in your design by considering the state diagram as shown in Fig. Q5(c).

Figure for Q5(c)

Figure for Q7(d)

(d) Write the Verilog code for full subtractor. (06)

(09)

(08)

- Q6. What are the benefits of state reduction? What can be achieved with proper state (a) (06)assignment?

- (b) Design a counter with repeated binary sequence 0, 1, 2, 4, 6. Use T Flip-flops. (10)

- The content of a 4 bit shift register is initially 1110. The register is shifted 6 times to the (05)(c) left with the serial input being 101101. What is the content of the register after each shift? (14)

- Design a serial 2's complementer. Use JK flip flop. (d)

- Q7. (a) Explain why we use both RAM's and PROM's in a system. (06)

- (b) How data is written into and read from magnetic core type memory. (09)

- What is race-around condition? How can it be overcome? Explain clearly. (c)

- Draw the state diagram for the circuit shown in Fig. Q7(d). Also find the state equation. (d) (11)

- Given the 11-bit data word 11001001010, generate the 15 bit Hamming code word. Q8. (a) (10)

- (b) Write a user defined primitive for a two input MUX in Verilog HDL.

- Draw the block diagram of a D/A converter. How does R-2R ladder network work as (c) (10)D/A converter?

- (d) What is FPGA? Draw the block diagram of FPGA architecture and describe its (07)operation.